A new type of computer memory merges storage and processing into one tunable array. Using special ferroelectric transistors (“MirrorBit” FeFETs), each cell can switch on-the-fly between simple storage, fast compute, dense multi-bit storage, and high-speed search (TCAM). The design cuts energy waste, boosts speed, and adapts in real time to tasks like AI training or rapid lookups all within the same hardware block.

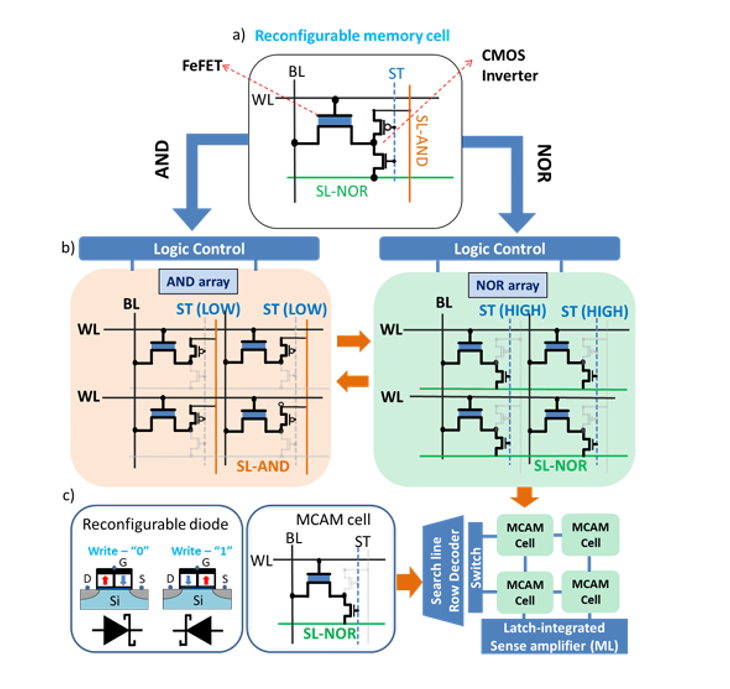

Figure (1a) Schematic of the reconfigurable memory cell showing a FeFET and CMOS inverter tied to SL-AND and SL-NOR with an ST line to switch modes; (1b) Arrays configured in AND-type under low ST bias and NOR-type under high ST bias; (1c) MirrorBit Source Write and Drain Write states modelled as a schottky diode and an MCAM cell array with search-line decoder and latch-integrated sense amplifiers

Today’s computers waste a lot of time and energy moving data between memory and processor. This creates delays, especially during tasks like AI and machine learning. Traditional memory systems also struggle to adapt to changing workloads and applications, making them inefficient for modern, data-heavy tasks.

- Fuses Memory and Logic in One Cell: Each cell holds data and performs simple operations, eliminating long data transfers and cutting latency.

- Reconfigures Modes Instantly: A single control line bias flips the entire array between AND-type (compute/storage) and NOR-type (search) without pausing operations.

- Stores Multiple Bits via MirrorBit: Special polarization states let each transistor act as 1-bit low-density, 1-bit fast-compute, 2-bit dense storage, or a reconfigurable Schottky-diode for TCAM.

- Enables High-Speed Searches: An XNOR/tri-state switch circuit supports two-step readouts, avoiding crosstalk and delivering rapid match/no-match results.

- Resource Allocation Dynamically: During AI training it can carve out compute-optimized cells, then later expand to maximize storage for inference or archival.

A laboratory prototype built on a small ferroelectric-memory bitcell (or reconfigurable memory cell) has been tested with precision waveform generators and Spice/TCAD simulations. Each MirrorBit FeFET’s write/read behaviors (UWL, UWH, SW, DW) and the AND/NOR mode switching have been electrically characterized, demonstrating stable multi-state storage and reliable search functionality.

The core circuit elements are validated in bench-scale hardware and detailed software models. Electrical tests confirm switching speed, multi-level storage, and TCAM searches.

4

By collapsing memory and compute into the same tiny chip area, this technology slashes the back-and-forth data traffic that normally burns up electricity. Data centers could see big cuts in their power bills and greenhouse-gas emissions, and battery-powered gadgets—like wearables or smart sensors—could run days or even weeks longer between charges. Faster on-chip processing also means AI features can respond in real time without offloading work to distant servers, improving user experiences in everything from voice assistants to autonomous vehicles. Over time, hardware that can switch roles on demand will stay useful far longer, so companies replace fewer boards and phones, cutting down on landfill waste and helping electronics recycling keep pace with demand.

- AI training and inference accelerators: In-memory compute boosts deep-learning speed

- Edge-computing and IoT devices: On-chip processing extends battery life

- Data-centre memory and search engines: In-memory search cuts energy and latency

- Network routing and packet-inspection hardware: Fast pattern matching without extra CPUs

- Automotive ADAS and real-time sensor fusion: Low-latency data merge for safer driving

Geography of IP

Type of IP

202421021083

565056