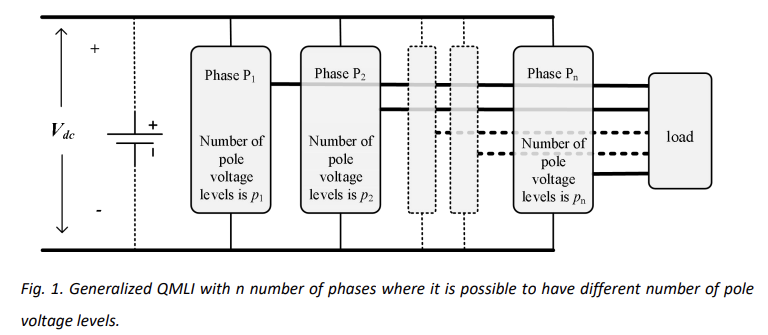

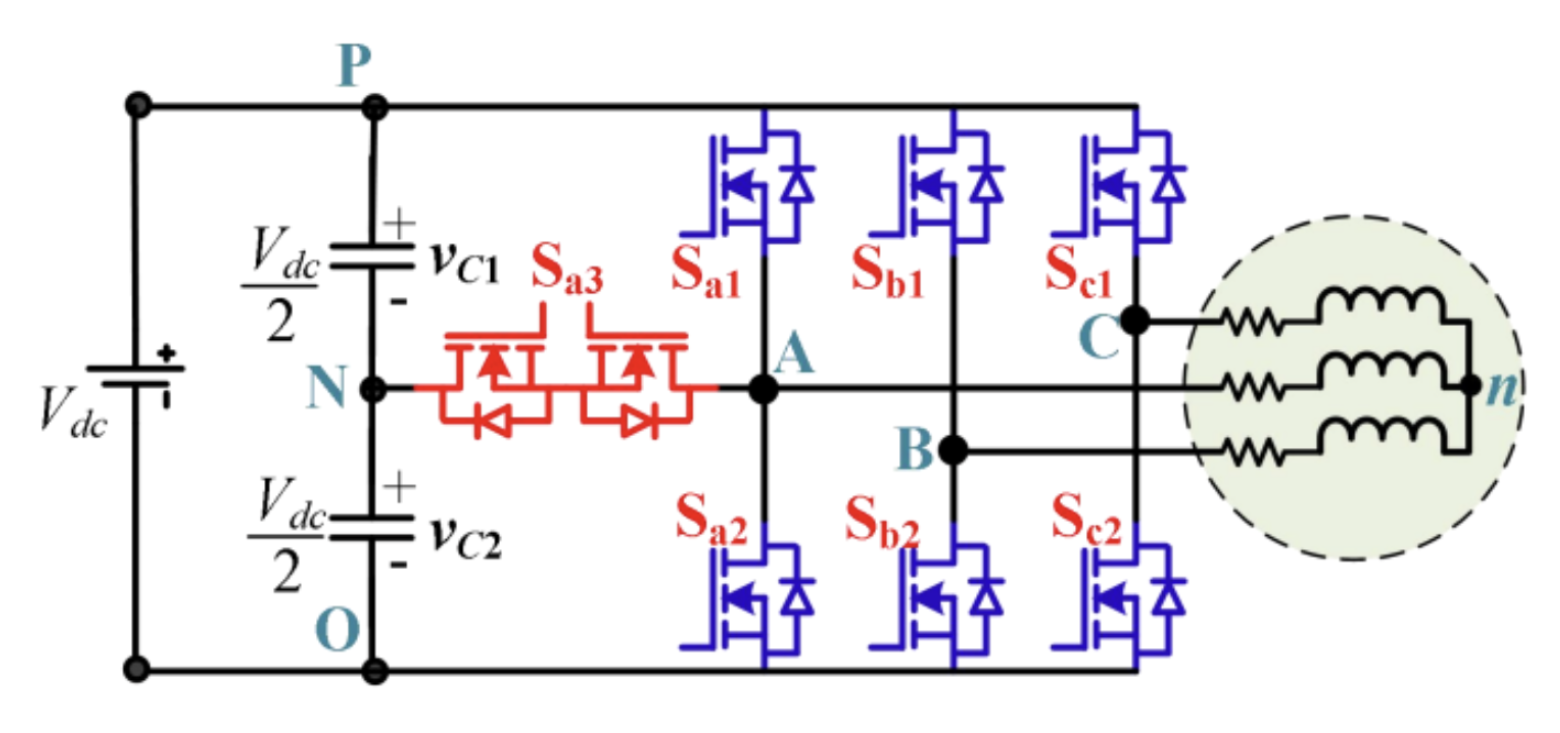

This invention introduces a new type of inverter called a Quasi Multilevel Inverter (QMLI) that simplifies traditional multilevel inverter designs. The QMLI uses an asymmetric approach, where one phase leg has more voltage levels than the others, effectively reducing common mode voltage (CMV) and leakage currents. This reduces electromagnetic interference and improves system efficiency without the high cost and complexity of conventional designs. The proposed QMLI is versatile, suitable for various applications like motor drives and solar energy systems, and ensures reliability and safety by minimizing harmful currents and voltage spikes. The novel design achieves significant performance benefits while remaining cost-effective and simpler to implement. A generalized schematic of the proposed topology is shown in Fig. 1. A specific implementation of the proposed topology is shown in Fig. 2.

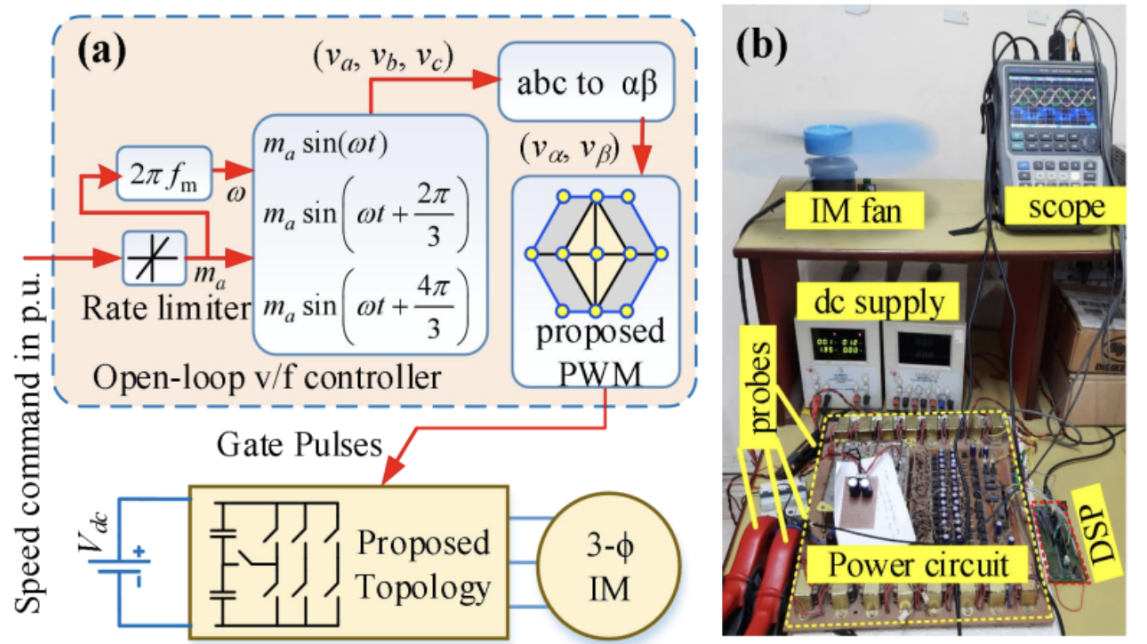

Figure (1) Generalized QMLI with a number of phases where it is possible to have different number of pole voltage levels. (2) The circuit schematic of a quasi 3-level inverter with the CMV reduction performance of a 3-level inverter but with a reduced switch count than a 3-level inverter.(3) (a) The schematic block diagram of the employed v/f control method where ω is the requency (in rad) and ma is the modulation index ; and(b) the image of the laboratory prototype.

Traditional multi-phase multilevel inverters, while effective in reducing Common mode voltage (CMV) and leakage currents, are complex and expensive due to the large number of components they require. This complexity increases cost, control difficulty, and system inefficiency. High-frequency switching in these inverters causes significant electromagnetic interference (EMI) and leakage currents, leading to potential equipment failure, increased energy losses, and safety hazards. Therefore, there is a need for a simpler, more cost-effective inverter design that can achieve similar reductions in CMV and leakage currents without the drawbacks of traditional multilevel inverters.

- Uses a novel Quasi Multi-Level Inverter (QMLI) topology where one phase leg produces a 3-level pole voltage and the other two legs produce 2-level pole voltages, reducing system complexity and cost.

- Introduces a new space vector (SV) diagram with 12 SVs, enabling a reduction in dv/dt of CMV by 50% and the CMV peak-to-peak value by 66.6%, enhancing system efficiency and performance.

- CMV and Leakage Current Reduction Achieves significant CMV reduction through its asymmetric pole voltage levels, leading to lower electromagnetic interference (EMI) and capacitive leakage current, improving system reliability and longevity.

- Generalized Extension to Multi-Phase Systems Can be generalized to multi-phase systems beyond the three-phase example, making it versatile and suitable for a wide range of industrial and renewable energy applications.

- Uses a novel PWM scheme to optimize the SV diagram, ensuring minimal CMV transitions, thus preventing issues like bearing currents and safety hazards in power electronic systems.

- Utilizes fewer components compared to conventional multilevel inverters, simplifying the design and maintenance processes while maintaining performance.

The proposed topology is simulated in PLECS software and the experimental results are obtained from a laboratory built prototype. IRF640 MOSFETs are used as the power semiconductor switches in the considered prototype and TI make TMS320F28335 processor is used to implement the PWM scheme and generate the gate pulses for control. A 3-phase induction motor, manufactured by EM Synergy, is used as the load with the following name plate parameters: i) frequency: 50Hz; ii) rated dc link voltage: 24V; iii) number of poles: 2; iv) peak phase current at full load: 1.83A; v) rated power: 13.6W; and vi) rated speed: 1120rpm. A simple open loop v/f control scheme is implemented along with the proposed PWM scheme (at 2kHz switching frequency) to operate the motor. The block diagram of the control logic and the picture of the hardware setup are shown in Fig. 7(a) and(b)respectively.

The design of the topology and the design of PWM scheme is completed. Complete system level concept has been developed and the topology and the PWM scheme are tested in simulation and hardware prototype in laboratory.

4

- Enhanced Safety in Solar PV Systems Reduces leakage current, preventing electrical hazards and increasing user safety.

- Increased Reliability of Industrial Equipment Reduces bearing currents in motor drives, decreasing the likelihood of equipment failure and extending the lifespan of industrial machinery.

- Cost-Effective Renewable Energy Integration Simplifies inverter design, making renewable energy solutions more affordable and accessible.

- Reduced Environmental Impact Enhances power electronics systems' efficiency, contributing to lower energy consumption and reduced carbon footprint.

- Support for Advanced Technological Applications Provides reliable and efficient power conversion for cutting-edge technologies, fostering innovation and technological advancement.

Power electronics, Renewable energy, Electric vehicles, Industrial automation, Semiconductor manufacturing

Renewable energy systems, Electric vehicles, Motor drives, Grid-tied solar PV systems, Uninterruptible power supplies, Industrial automation, Power distribution systems

202221006502

418210