Recent advancements in full-duplex communication channels have the potential to significantly enhance data transmission rates and network efficiency by enabling simultaneous transmission and reception over the same frequency band. However, this technique poses a critical challenge of self-interference (SI) and echo, where the receiver is degraded by its own transmitted signals. The SI and echo can lead to significant performance degradation and require efficient cancellation techniques. This invention addresses the need for a robust and dynamic system to cancel SI and echo in full-duplex wireline communication links, ensuring reliable data transmission without degrading the channel performance.

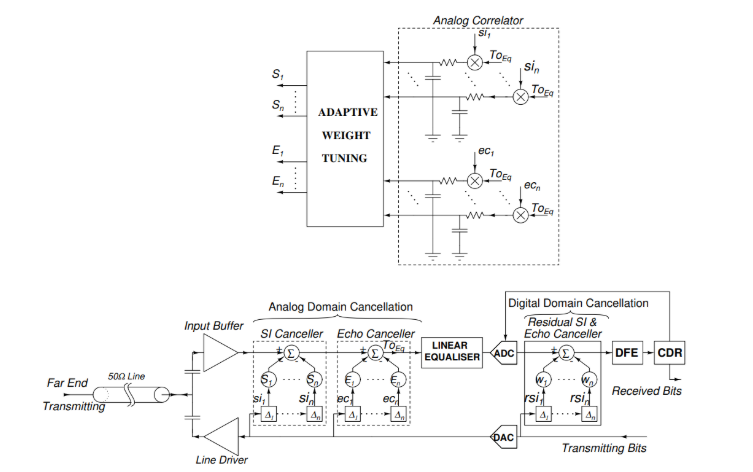

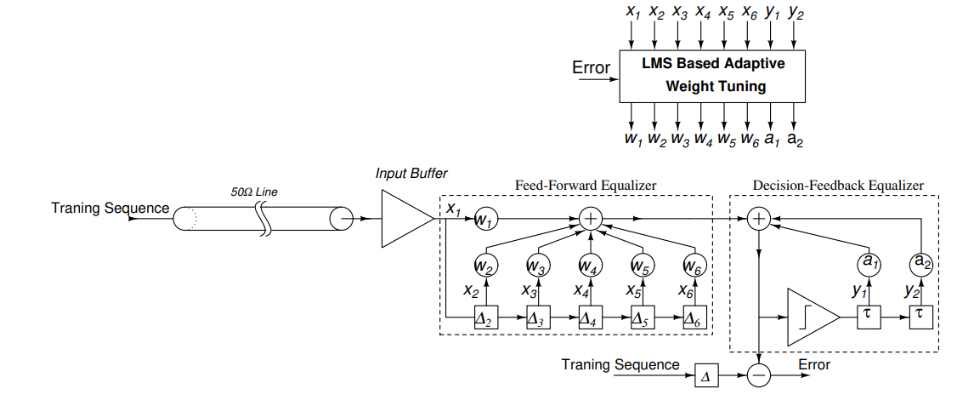

This invention provides a novel system for cancelling self-interference (SI) and echo in full-duplex wireline communication links. The system consists of a transceiver at each end of the communication link, equipped with a self-interference canceller module and an echo canceller module. Both modules operate in the analog domain, effectively reducing SI and echo, and a residual SI and echo cancellation module handles any remaining interference in the digital domain. The adaptive nature of the canceller modules ensures that the system can adjust itself in real-time without requiring additional training sequences, thus reducing the overall overhead and improving the efficiency of full-duplex communication.

- Adaptive Interference Canceller: The system uses adaptive algorithms to dynamically adjust the weight coefficients of the canceller modules, ensuring efficient cancellation of SI and echo.

- Real-Time Cancellation: Both the SI and echo canceller modules operate in the analog domain, allowing real-time cancellation without any pauses in data transmission.

- Hybrid Analog-Digital Approach: The system employs a combination of analog and digital cancellation techniques, where the analog canceller handles most of the cancellation and the digital canceller addresses residual interference.

- Robust and Scalable: The modules are fabricated on a single integrated chip, making the system robust and scalable for various applications.

The prototype consists of a full-duplex wireline communication channel with two transceivers, one at each end. Each transceiver is equipped with a SI canceller module and an echo canceller module. The system operates on a 10 meters channel with 10% impedance mismatch at a data rate of 10 Gbps. Testing was carried out using the system on both single and multiple transmission scenarios, demonstrating its effectiveness in cancelling SI and echo.

A semiconductor chip based prototype has been demonstrated.

4

The invention enables the efficient and reliable operation of full-duplex communication links, reducing self-interference and echo. This leads to improved performance and reduced power consumption, making it highly beneficial for telecommunications, cable modems, and other high-speed data communication systems. By enhancing data transmission rates and network efficiency, the technology supports the needs of modern communication infrastructure, contributing to advancements in data centers, edge computing, and AI applications.

- Telecommunications

- Cable Modems

- Data Centers

- Edge Computing

- High-Speed Networks

Geography of IP

Type of IP

16/914,628

11431367