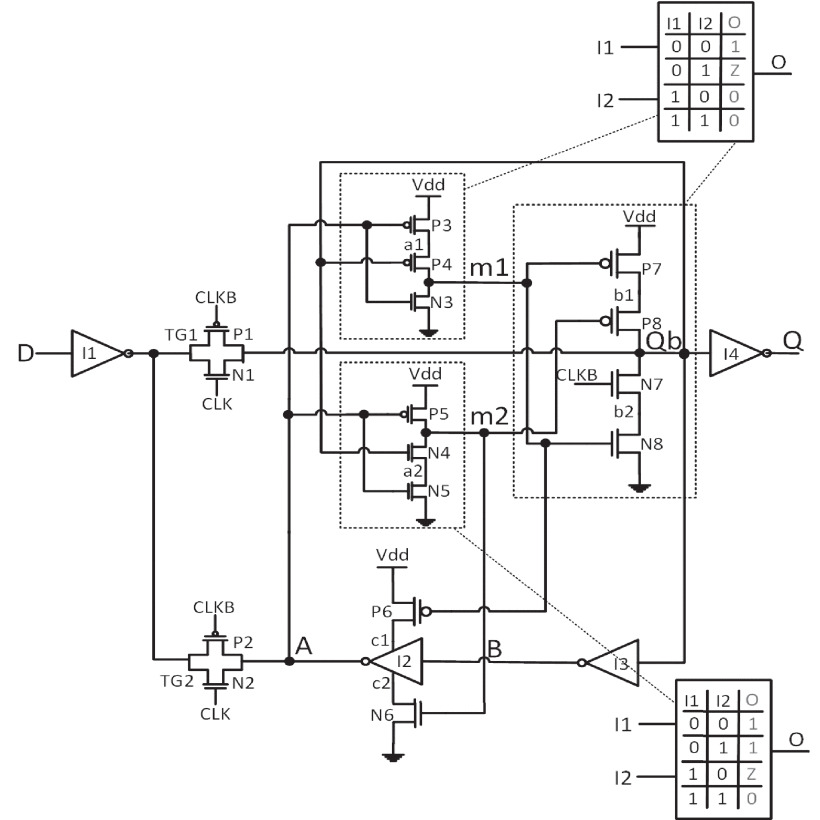

The invention disclosed is a latch designed to withstand single event soft errors (SEs), particularly in digital circuits vulnerable to transient faults caused by cosmic rays or alpha particles. It features a flexible architecture comprising different configurations of p-channel and n-channel transistors (1P-2N or 2P-1N), coupled with auxiliary elements like back-to-back inverters or 3-input C-elements. A clocked circuit module ensures proper timing, enabling the latch to operate in transparent mode for writing data and in hold mode for storing data securely. This SE-tolerant design aims to mitigate soft errors in memory cells and sequential logic, enhancing reliability in scaled-down digital circuits prone to environmental disturbances.

In digital circuits, particularly those used in sensitive applications like space exploration or medical devices, tiny particles from outer space or even within our atmosphere can cause temporary glitches or errors. These glitches, called single event soft errors (SEs), can disrupt how circuits store or process information, potentially leading to incorrect data or system failures. This creates a challenge in creating circuits, like latches, that can continue working correctly despite these occasional disturbances.

- Adaptive Resilience: This innovation integrates multiple transistor configurations (1P-2N and 2P-1N) for adaptive resilience against soft errors.

- Enhanced Error Detection: It utilizes auxiliary elements such as back-to-back inverters and 3-input C-elements for enhanced error detection.

- Precise Timing: It includes clocked circuit modules to ensure precise timing for data storage and retrieval.

- Dual Modes: It operates in both transparent and hold modes, facilitating seamless data writing and stable storage.

- SE Mitigation: It addresses single event SEs in digital circuits, crucial for reliability in space and medical technology.

- Configuration Flexibility: It offers flexibility in configuration to optimize performance based on specific application requirements.

The complete circuit is simulated and the results are demonstrated using circuit simulation.

3

This innovation enhances reliability of medical devices and space exploration technology by reducing errors caused by environmental factors. It also improves data accuracy in critical applications, ensuring safety and efficiency in digital systems used in healthcare and aerospace industries.

- Aerospace and Defense: Used in spacecraft electronics to ensure reliability and accuracy of data transmission

- Biomedical: Applied in medical equipment to maintain consistent performance and data integrity during patient monitoring

- Other Industries: Semiconductors

Geography of IP

Type of IP

2806/MUM/2015

452539